Ahh yes, Hub = 1GB while WP2=2GB. I'll need to go build that image..

Official LE13 Test Images for Amlogic (Kodi-22)

-

chewitt -

May 19, 2024 at 7:03 AM -

Thread is Unresolved

-

-

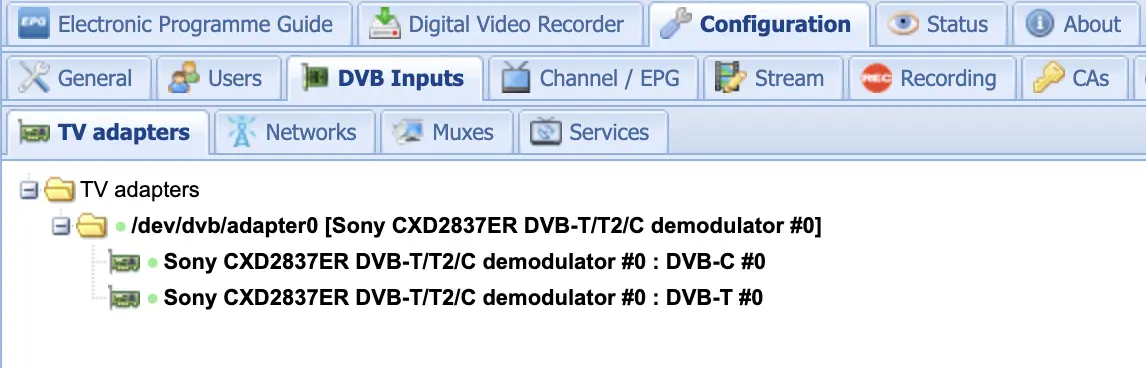

Using some initial work from https://github.com/mczerski - Claude and I (mostly Claude) have made some progress on mainline DVB support: https://paste.libreelec.tv/moving-lab.log .. the above is from a WeTek Play2 box.

Before anyone gets wildly excited, the vendor kernel demux driver that Marek started porting is a festering ifdef nightmare that looks like it needs a lot of work and I have no way to test DVB-C, DVB-T, or DVB-S things; so I have no clue if the now-showing-up adapters do more than look pretty. Marek appears to have more of a clue about DVB things than me so cross fingers

NB: I plan to dig out the DVB-S module for WP2 and an old O2.cz box that I have in a cupboard somewhere and get those working next. Once that's done I'll clean up the smorgasbord of patches, push branches to GitHub, and share some updated images.

-

Hi everyone,

I’ve managed to get the Amlogic mainline DVB driver working using software PID filtering. Currently, on the SM1 (S905X3 mecool K5 and magicsee c500 pro), it successfully detects and operates all Amlogic DVB modules and frontends using a single dmx0 driver. I have developed this according to modern kernel architecture. No high cpu usages. but libreelec vdec mpeg2 does not decode mpeg4 hw accelerations. software based decoding mpeg2 ok. But the video quality is not very good. It has nothing to do with the dvb driver anyway. But it streams perfectly to devices on the network.

However, I haven't been able to get dmx1 and dmx2 working yet, as I haven't identified the correct offsets. Once those are functional and stable, I intend to share the full driver with the community. It works flawlessly on single-frontend devices and is compatible with the upstream mainline kernel.

I have also drafted a new driver version for hardware PID filtering based on the vendor kernel architecture. If I can get the HW PID filter operational, I will share that as well. I believe this version serves as a solid starting point for further development."

Code

Display MoreLibreELEC:~ # uname -a Linux LibreELEC 6.19.0 #1 SMP Fri Mar 13 02:03:55 +03 2026 aarch64 GNU/Linux LibreELEC:~ # dmesg | grep -i dvb [ 10.600472] amlogic-dvb ffd06000.dvb: TS registers: [mem 0xffd06000-0xffd063ff] [ 10.600498] amlogic-dvb ffd06000.dvb: No 'demux' region — SM1: using 'ts' base (0xffd06000) for DMX registers [ 10.600603] amlogic-dvb ffd06000.dvb: Async FIFO registers: [mem 0xffd09000-0xffd0afff] [ 10.600714] debugfs: 'ffd06000.dvb-demux' already exists in 'regmap' [ 10.600760] amlogic-dvb ffd06000.dvb: Detected SM1 (S905X3/D3): 3 demux, 3 TS inputs, 32 PID filters, 2 async FIFO, 192 Mbps max [ 10.600768] amlogic-dvb ffd06000.dvb: CI+ support available [ 10.600791] amlogic-dvb ffd06000.dvb: Performing hardware reset [ 10.609896] amlogic-dvb ffd06000.dvb: Hardware reset completed [ 10.609959] amlogic-dvb ffd06000.dvb: rst_demux_top reset OK [ 10.610024] amlogic-dvb ffd06000.dvb: GPIO: 0 GPIO kaydedildi, /sys/kernel/debug/gpio'da görünür [ 10.610036] amlogic-dvb ffd06000.dvb: pinctrl: TS pin state aktif → /sys/kernel/debug/pinctrl [ 10.611856] dvbdev: DVB: registering new adapter (Amlogic DVB) [ 10.611878] amlogic-dvb ffd06000.dvb: ts_hw_init: starting [ 10.611886] amlogic-dvb ffd06000.dvb: ts_hw_init: initializing TS input 0/3 [ 10.611898] amlogic-dvb ffd06000.dvb: ts_input_init: TS input 0 DTS'de disabled, atlanıyor [ 10.611903] amlogic-dvb ffd06000.dvb: ts_hw_init: initializing TS input 1/3 [ 10.612013] amlogic-dvb ffd06000.dvb: ts_input_init: TS1 ts_control=0x000 [ 10.612019] amlogic-dvb ffd06000.dvb: ts_input_init: TS input 1 → PARALLEL mode [ 10.612024] amlogic-dvb ffd06000.dvb: ts_input_init: initializing TS input 1 [ 10.612040] amlogic-dvb ffd06000.dvb: ts_input_init: TS input 1 OK (mode=0x30003 fec_ctrl=0x000 s2p_id=-1 clk_inv=0) [ 10.612047] amlogic-dvb ffd06000.dvb: ts_hw_init: initializing TS input 2/3 [ 10.612053] amlogic-dvb ffd06000.dvb: ts_input_init: TS input 2 DTS'de disabled, atlanıyor [ 10.612058] amlogic-dvb ffd06000.dvb: ts_hw_init: initializing S2P 0/2 [ 10.612063] amlogic-dvb ffd06000.dvb: s2p_init: starting S2P 0 [ 10.612077] amlogic-dvb ffd06000.dvb: s2p_init: writing S2P 0 ctrl=0xcccc [ 10.612082] amlogic-dvb ffd06000.dvb: ts_hw_init: initializing S2P 1/2 [ 10.612086] amlogic-dvb ffd06000.dvb: s2p_init: starting S2P 1 [ 10.612101] amlogic-dvb ffd06000.dvb: s2p_init: writing S2P 1 ctrl=0xcccc [ 10.612107] amlogic-dvb ffd06000.dvb: ts_hw_init: writing TS_TOP_CONFIG = 0x7700bb47 (sync_byte=0x47, packet_len=188) [ 10.612113] amlogic-dvb ffd06000.dvb: ts_hw_init: completed successfully [ 10.612131] amlogic-dvb ffd06000.dvb: asyncfifo_init: HW reset OK [ 10.612135] amlogic-dvb ffd06000.dvb: asyncfifo_init: starting, num=2 [ 10.612140] amlogic-dvb ffd06000.dvb: asyncfifo_init: initializing FIFO 0 [ 10.612257] amlogic-dvb ffd06000.dvb: FIFO 0: DVR rb OK (4 MB) [ 10.612266] amlogic-dvb ffd06000.dvb: afifo0: allocating coherent buffer (262144 bytes) [ 10.613506] amlogic-dvb ffd06000.dvb: afifo0: dma buffer virt=00000000f1542136 dma=0x0000000048440000 [ 10.613539] amlogic-dvb ffd06000.dvb: afifo0: REG0 (DMA addr) = 0x48440000 [ 10.613545] amlogic-dvb ffd06000.dvb: afifo0: REG1 reset pulse = 0x00600800 (flush_cnt=0x800) [ 10.613551] amlogic-dvb ffd06000.dvb: afifo0: REG1 (WRAP+FLUSH) = 0x00300800 [ 10.613557] amlogic-dvb ffd06000.dvb: afifo0: REG2 (FILL_EN, no src) = 0x00300000 [ 10.613562] amlogic-dvb ffd06000.dvb: afifo0: REG3 (IRQ thresh) = 0x2001ff (every 64KB) [ 10.613568] amlogic-dvb ffd06000.dvb: Async FIFO 0: base=0x0000000048440000 size=262144 flush=65536 REG1=0x00300800 CPU0 [ 10.613575] amlogic-dvb ffd06000.dvb: asyncfifo_init: initializing FIFO 1 [ 10.613725] amlogic-dvb ffd06000.dvb: FIFO 1: DVR rb OK (4 MB) [ 10.613736] amlogic-dvb ffd06000.dvb: afifo1: allocating coherent buffer (262144 bytes) [ 10.614030] amlogic-dvb ffd06000.dvb: afifo1: dma buffer virt=000000004cfdb751 dma=0x0000000048480000 [ 10.614054] amlogic-dvb ffd06000.dvb: afifo1: kept idle (vendor behaviour) [ 10.614059] amlogic-dvb ffd06000.dvb: Async FIFO 1: base=0x0000000048480000 size=262144 flush=65536 ctrl=0x00000000 CPU1 [ 10.614067] amlogic-dvb ffd06000.dvb: dsc0: init OK [ 10.614072] amlogic-dvb ffd06000.dvb: dsc1: init OK [ 10.614077] amlogic-dvb ffd06000.dvb: dmx0: hw_init [ 10.614269] amlogic-dvb ffd06000.dvb: dmx0: sec_buf OK 131072 bytes phys=0x48420000 base=0x4842 [ 10.614281] amlogic-dvb ffd06000.dvb: dmx0: sec_buf grp0=0x48420000 grp1=0x48428000 grp2=0x48430000 grp3=0x48438000 [ 10.614405] amlogic-dvb ffd06000.dvb: dmx0: PES buf OK phys=0x48410000 [ 10.614679] amlogic-dvb ffd06000.dvb: dmx0: subtitle buf OK phys=0x484c0000 len=65536 [ 10.614696] amlogic-dvb ffd06000.dvb: dmx0: hw_init OK [ 10.618161] amlogic-dvb ffd06000.dvb: dmx0: IRQ 28 [ 10.618421] amlogic-dvb ffd06000.dvb: dmx0: IRQ 28 registered OK [ 10.618437] amlogic-dvb ffd06000.dvb: dmx1: hw_init [ 10.618904] amlogic-dvb ffd06000.dvb: dmx1: sec_buf OK 131072 bytes phys=0x484e0000 base=0x484e [ 10.618923] amlogic-dvb ffd06000.dvb: dmx1: sec_buf grp0=0x484e0000 grp1=0x484e8000 grp2=0x484f0000 grp3=0x484f8000 [ 10.619014] amlogic-dvb ffd06000.dvb: dmx1: PES buf OK phys=0x484d0000 [ 10.619179] amlogic-dvb ffd06000.dvb: dmx1: subtitle buf OK phys=0x48500000 len=65536 [ 10.619192] amlogic-dvb ffd06000.dvb: dmx1: hw_init OK [ 10.619759] amlogic-dvb ffd06000.dvb: dmx1: IRQ 29 [ 10.620296] amlogic-dvb ffd06000.dvb: dmx1: IRQ 29 registered OK [ 10.620318] amlogic-dvb ffd06000.dvb: dmx2: hw_init [ 10.621058] amlogic-dvb ffd06000.dvb: dmx2: sec_buf OK 131072 bytes phys=0x48520000 base=0x4852 [ 10.621080] amlogic-dvb ffd06000.dvb: dmx2: sec_buf grp0=0x48520000 grp1=0x48528000 grp2=0x48530000 grp3=0x48538000 [ 10.621323] amlogic-dvb ffd06000.dvb: dmx2: PES buf OK phys=0x48510000 [ 10.626612] amlogic-dvb ffd06000.dvb: dmx2: subtitle buf OK phys=0x48540000 len=65536 [ 10.626636] amlogic-dvb ffd06000.dvb: dmx2: hw_init OK [ 10.631951] amlogic-dvb ffd06000.dvb: dmx2: IRQ 30 [ 10.632660] amlogic-dvb ffd06000.dvb: dmx2: IRQ 30 registered OK [ 10.632777] amlogic-dvb ffd06000.dvb: afifo0: IRQ 31 [ 10.632808] amlogic-dvb ffd06000.dvb: afifo0: IRQ 31 registered OK [ 10.632820] amlogic-dvb ffd06000.dvb: DEMUX_CONTROL(0) after IRQ setup = 0xc0000000 [ 10.632829] amlogic-dvb ffd06000.dvb: DVB adapter global listeye eklendi [ 10.632835] amlogic-dvb ffd06000.dvb: DVB adapter ready, expecting 1 frontend(s) [ 10.632842] amlogic-dvb ffd06000.dvb: [0] /soc/bus@ffd00000/i2c@1c000/dvb-frontend@14 [ 10.632947] debugfs: 'gpio' already exists in 'ffd06000.dvb' [ 10.632958] debugfs: 'pinctrl_state' already exists in 'ffd06000.dvb' [ 10.632971] amlogic-dvb ffd06000.dvb: sec_watchdog: başlatıldı (250ms) [ 10.632978] amlogic-dvb ffd06000.dvb: amlogic-dvb V2.54 loaded [ 10.707889] avl6862 3-0014: GPIO: amlogic-dvb-fe0-power → /sys/kernel/debug/gpio [ 10.707935] avl6862 3-0014: GPIO: amlogic-dvb-fe0-reset → /sys/kernel/debug/gpio [ 12.242544] amlogic-dvb ffd06000.dvb: runtime_resume: enabling clocks [ 12.242556] amlogic-dvb ffd06000.dvb: ts_hw_init: starting [ 12.242564] amlogic-dvb ffd06000.dvb: ts_hw_init: initializing TS input 0/3 [ 12.242573] amlogic-dvb ffd06000.dvb: ts_input_init: TS input 0 DTS'de disabled, atlanıyor [ 12.242579] amlogic-dvb ffd06000.dvb: ts_hw_init: initializing TS input 1/3 [ 12.242589] amlogic-dvb ffd06000.dvb: ts_input_init: TS1 ts_control=0x000 [ 12.242595] amlogic-dvb ffd06000.dvb: ts_input_init: TS input 1 → PARALLEL mode [ 12.242600] amlogic-dvb ffd06000.dvb: ts_input_init: initializing TS input 1 [ 12.242616] amlogic-dvb ffd06000.dvb: ts_input_init: TS input 1 OK (mode=0x30003 fec_ctrl=0x000 s2p_id=-1 clk_inv=0) [ 12.242621] amlogic-dvb ffd06000.dvb: ts_hw_init: initializing TS input 2/3 [ 12.242627] amlogic-dvb ffd06000.dvb: ts_input_init: TS input 2 DTS'de disabled, atlanıyor [ 12.242632] amlogic-dvb ffd06000.dvb: ts_hw_init: initializing S2P 0/2 [ 12.242636] amlogic-dvb ffd06000.dvb: s2p_init: starting S2P 0 [ 12.242651] amlogic-dvb ffd06000.dvb: s2p_init: writing S2P 0 ctrl=0xcccc [ 12.242655] amlogic-dvb ffd06000.dvb: ts_hw_init: initializing S2P 1/2 [ 12.242660] amlogic-dvb ffd06000.dvb: s2p_init: starting S2P 1 [ 12.242674] amlogic-dvb ffd06000.dvb: s2p_init: writing S2P 1 ctrl=0xcccc [ 12.242681] amlogic-dvb ffd06000.dvb: ts_hw_init: writing TS_TOP_CONFIG = 0x7700bb47 (sync_byte=0x47, packet_len=188) [ 12.242686] amlogic-dvb ffd06000.dvb: ts_hw_init: completed successfully [ 12.242704] amlogic-dvb ffd06000.dvb: DVB: registering adapter 0 frontend 0 (Availink avl6862)... [ 12.245431] amlogic-dvb ffd06000.dvb: dmx0: kaynak=2 STB_TOP=0x00040000 FEC_CTRL=0x00000000 [ 12.245466] amlogic-dvb ffd06000.dvb: Demux 0 <- tsin_b (AML_TS_SRC_FRONTEND_TS1) [ 12.245474] amlogic-dvb ffd06000.dvb: afifo0: REG2 source=0 val=3 reg2=0x01b00000 [ 12.245485] amlogic-dvb ffd06000.dvb: afifo0: REG2 readback=0x03b00000 FILL=1 SRC=3 [ 12.245491] amlogic-dvb ffd06000.dvb: Async FIFO 0 source set to demux 0 [ 12.245498] amlogic-dvb ffd06000.dvb: TS rate set to 54 Mbps [ 12.245502] amlogic-dvb ffd06000.dvb: Frontend 0 registered (demod-initiated) [ 14.041314] i2c i2c-3: Load avl6862 firmware patch for DVB-S/S2 size=44108 [ 17.160632] Modules linked in: ir_rc6_decoder ir_nec_decoder 8021q bluetooth ecdh_generic ecc panfrost governor_simpleondemand drm_shmem_helper rtw88_8822cs rtw88_8822c rtw88_sdio rtw88_core mac80211 snd_usb_audio snd_hwdep snd_usbmidi_lib snd_rawmidi meson_ir rtc_meson_vrtc meson_vdec(C) cfg80211 rfkill avl6862(O) amlogic_dvb(O) r912(O) r848(O) pkcs8_key_parser fuse nfnetlink [ 19.234123] amlogic-dvb ffd06000.dvb: DVB: adapter 0 frontend 0 frequency 0 out of range (175000000..2150000000) [ 19.239717] i2c i2c-3: Load avl6862 firmware patch for DVB-S/S2 size=44108 LibreELEC:~ # dmesg | grep -i gpio [ 0.130040] irq_meson_gpio: 100 to 8 gpio interrupt mux initialized [ 0.184374] pwrseq_emmc emmc-pwrseq: EMMC reset pin tied to a sleepy GPIO driver; reset on emergency-reboot disabled [ 0.449675] meson-gx-mmc ffe05000.mmc: Got CD GPIO [ 10.610024] amlogic-dvb ffd06000.dvb: GPIO: 0 GPIO kaydedildi, /sys/kernel/debug/gpio'da görünür [ 10.632947] debugfs: 'gpio' already exists in 'ffd06000.dvb' [ 10.707889] avl6862 3-0014: GPIO: amlogic-dvb-fe0-power → /sys/kernel/debug/gpio [ 10.707935] avl6862 3-0014: GPIO: amlogic-dvb-fe0-reset → /sys/kernel/debug/gpio [ 12.240599] avl6862 3-0014: fe0: GPIO sekans tamam (pwr_off=100 pwr_on=300 rst=600+500 ms) -

taki Interesting! .. but I would ask that you push current working code to a GitHub repo as it would make a lot of sense for Marek (and likely others) to collaborate on a clean demux rewrite that could eventually be upstreamed, than get too far down the road of reworking vendor code.

NB: I have been poking around in the vdec code recently and have one MPEG2 video that now decodes (badly) which I guess is an improvement on no videos decoding. I have a hunch the underlying issue is about alignment of buffers to frame dimensions, but neither I or Claude managed to spot the problem yet. It continues to be something I tinker with (among many things) though.

-

I think we must decide how we approach this topic. The work I did was more like a proof of concept that it is even possible to have DVB working under mainline kernel. To make it real it must be merged into upstream.

taki You said:

I have developed this according to modern kernel architecture.

Is that mean that You wrote it from scratch or did You take the vendor driver and adapted it like I did ?

One thing is to write driver code according to mainline kernel infrastructure, other thing is to have this driver merged into upstream. I do not have expirience in pushing code to mainline kernel but I think that the code from my branch is far from this goal

-

Ahh, rozpruwacz is Marek

I now have the DVB-S and DVB-T tuners for the WeTek Play2 and the DVB-T tuner in the O2.cz box showing up in Tvheadend. I am able to run a scan without errors. However I have no Satellite dish or Terrestrial antenna to connect them to so all scans find zero services (as expected) so it's impossible to tell whether anything is really working

I've pushed an updated set of images to my testing share. The WP2 image and 'box' image will boot the default WP2 device-tree which contains no DVB support, so you will need to edit extlinux.conf or uEnv.ini and change the dtb name to one of:

- meson-gxbb-wetek-play2-atsc.dtb <= might not work, I didn't find the ATSC tuner module to test yet

- meson-gxbb-wetek-play2-dvb-s.dtb

- meson-gxbb-wetek-play2-dvb-t.dtb

The O2.cz box (SML-5442TW) and the GTMEDIA GTT-2 box Marek has been using both have DVB support enabled.

Once WP2 is rebooted with the correct device-tree file dmesg should show the cards, and you can install Tvheadend43 (or VDR) to scan for services. I'm a bit vague on the remaining process as (as mentioned) I can't test anything.

rawnar I've also included a WeTek Hub image in the test share. Apologies for the long wait, I got a bit distracted.

-

Of course, I didn't write the driver from scratch. I’m not a professional programmer or developer; I’m doing this as a hobby. You likely know coding much better than I do. That said, I’m not completely clueless about Linux and C++; it would be impossible to create a driver of this complexity without at least some understanding. My goal isn't to upstream anything; it’s simply to enable DVB streaming since USB tuner prices have become so expensive.

Using the sti driver (from the Google Git kernel common) as a reference, I used DeepSeek to generate the backbone and developed the driver step-by-step by fixing numerous bugs. One of the biggest problems is that most of the demos and tuners used by amlogic devices are not available in the mainline kernel. While testing the driver, it was not possible to know whether the presence or absence of signal was due to the dvb driver or the frontend. Sometimes fake signal and i2c error etc. It was like looking for a needle in a haystack. Honestly, this could be a PhD thesis topic: creating a functional kernel module in a complex structure using guided AI. I conducted many tests, including address verification via devmem, etc.

The final piece of the puzzle is AML_MEM_REQ_EN_SW—everything works with it. However, it fails with AML_MEM_REQ_EN_HW. The software driver works perfectly on the S905X3 because that’s the device I have for testing. I can't guarantee it will work for chips newer than the S905X3 without the hardware on hand, but I believe rozpruacz can make it happen. I actually got into this because of the 'S905X4 built-in DVB' topic on the CoreELEC forum. He helped me a lot; without his guidance, I probably wouldn't have started this.

I had stepped away from Linux development for quite a while. To continue, I prepared this as a LibreELEC addon (similar to the avl6862 addon in CoreELEC) without touching the mainline kernel. The advantage is that you can add patches and compile easily without messing with Kconfig, etc. Plus, you can send the newly compiled driver and DTB to the device over the network for testing.

I also have an old S905 Mecool K2 Pro. There are minor differences; it has demod and tuner signal lock, but it needs small offset corrections compared to the S905 for the TS (Transport Stream) to flow. In short, I’m currently working on the HW demux and will share it as soon as possible. Here, architecture comes into play again: whether the demod/tuner will connect directly or via the DTS driver. There are specific wait times for the Amlogic hardware to become active.

Code

Display Morestatic const struct of_device_id aml_dvb_of_match[] = { /* S905 (GXBB) */ { .compatible = "amlogic,gxbb-dvb" }, /* S905X/D/W (GXL) */ { .compatible = "amlogic,gxl-dvb" }, /* S912 (GXM) */ { .compatible = "amlogic,gxm-dvb" }, /* S905X2/D2 (G12A) */ { .compatible = "amlogic,g12a-dvb" }, /* S922X/A311D (G12B) */ { .compatible = "amlogic,g12b-dvb" }, /* S905X3/D3 (SM1) */ { .compatible = "amlogic,sm1-dvb" }, /* T962X3 (TL1) */ { .compatible = "amlogic,tl1-dvb" }, /* S905X4/D4 (SC2) */ { .compatible = "amlogic,sc2-dvb" }, /* T950X4/A311D2 (T7) */ { .compatible = "amlogic,t7-dvb" }, { /* sentinel */ } }; MODULE_DEVICE_TABLE(of, aml_dvb_of_match); -

I pushed my current working DVB patches branch to https://github.com/chewitt/linux/commits/dvb-7.0.y/

I pushed current AMLGX working image changes to https://github.com/chewitt/LibreELEC.tv/commits/amlogic

To make image packaging easier I have the Linux patchset I'm testing in projects/Amlogic/patches/linux and a separate set of DVB patches in packages/linux/patches/dvb as this makes it simple to regenerate each patchset independently (using a script) and then I can respin the image to test changes. Thanks to an ex-employer that went bust I'm lucky to have a 32x core build server so image respin time (only rebuilding the kernel) is around 2 mins; then I pull the image from the server to the current test device over scp and reboot to see what broke/changed/etc. and then give feedback to Claude. NB: If you ever wondered why I always hardcode a static version in all my test images; it means I can predict filenames on a remote server to make transfers easier.

-

rawnar I've also included a WeTek Hub image in the test share. Apologies for the long wait, I got a bit distracted.

Found it.

You beat me to it. I almost had my old linux installation up and running again to build the image myself.

You beat me to it. I almost had my old linux installation up and running again to build the image myself.I placed it on a SD-Card and booted the system. Attached you can find the output I recorded from the UART. Spoiler: No strange characters coming from the UART and the system has booted now several times without halting during boot. So, the fix you made 1 year ago works

.

.Other thinks you like to see tested on the Wetek Hub?

-

To detect the reset power, i2c pin and active ts pins of the dvb driver, first connect to the android own software with adb and cat /sys/kernel/debug/pinctrl/*/pinmux-pins

Get the device information with cat /sys/kernel/debug/pinctrl/*/pinmux-functions and edit the mainline dts accordingly. You may need to shut down some nodes or redirect them to the correct pin due to pin conflict. I gave the driver as an addon. Copy the AVL6862 folder under LibreELEC.tv/packages/linux-driver-addons/dvb/ and add PROJECT=Amlogic DEVICE=AMLGX ARCH=aarch64 ./scripts/create_addon AVL6862 compile. Of course, if the dts is not correct, the driver probe will not occur. Maybe you can take it one step further.good lucksample dts

C

Display More// SPDX-License-Identifier: (GPL-2.0+ OR MIT) /* * MeCool K5 DVB DTS - V2.57 * * V2.49 değişiklikleri: * - Clock sırası Android DTB ile uyumlu: demux, ahbarb0, parser_top * - Resets: RESET_DEMUX/ASYNC0/ASYNC1/DEMUX_TOP (meson-g12a-reset.h) * - Reset include eklendi * * Donanim: * AVL6862 demod (Rafael R848 tuner) * -> GPIOZ pinleri, tsin_b, 8-bit paralel -> SM1 TS1 (FEC_SEL=1) * -> i2c3 (SDA=GPIOA_14, SCK=GPIOA_15) * Reset : GPIOAO_10 (ACTIVE_LOW) * Power : GPIOE_2 / aobus offset 14 (ACTIVE_HIGH) * * SM1 register haritasi (devmem2 dogrulandi): * "ts" : 0xFFD06000-0xFFD063FF * "async-fifo": 0xFFD09000-0xFFD0AFFF * * IRQ (GIC_SPI = GIC_HW - 32, IRQ_TYPE_EDGE_RISING zorunlu): * GIC SPI 23 -> demux0 (HW55) * GIC SPI 5 -> demux1 (HW37) * GIC SPI 21 -> demux2 (HW53) * GIC SPI 19 -> asyncfifo0 (HW51) * GIC SPI 25 -> asyncfifo1 (HW57) * * ONEMLI: SM1'de EDGE_RISING kullan! LEVEL_HIGH ile * AsyncFIFO IRQ gelmiyor → veri akışı tamamen durur. */ /dts-v1/; #include "meson-sm1-ac2xx.dtsi" #include <dt-bindings/gpio/gpio.h> #include <dt-bindings/gpio/meson-g12a-gpio.h> #include <dt-bindings/interrupt-controller/irq.h> #include <dt-bindings/interrupt-controller/arm-gic.h> #include <dt-bindings/clock/g12a-clkc.h> #include <dt-bindings/reset/amlogic,meson-g12a-reset.h> / { compatible = "videostrong,mecool-k5", "amlogic,sm1"; model = "VIDEOSTRONG MeCool K5"; memory@0 { device_type = "memory"; reg = <0x0 0x0 0x0 0x80000000>; /* 2GB */ }; aliases { i2c3 = &i2c3; }; }; /* GPIOAO_10 (reset pini) ile cakisiyor */ &pwm_AO_ab { status = "disabled"; }; /* I2C3: AVL6862 */ &i2c3 { status = "okay"; pinctrl-0 = <&i2c3_sda_a_pins>, <&i2c3_sck_a_pins>; pinctrl-names = "default"; clock-frequency = <100000>; frontend0: dvb-frontend@14 { compatible = "availink,avl6862"; reg = <0x14>; status = "okay"; reset-gpios = <&gpio_ao 10 GPIO_ACTIVE_LOW>; power-gpios = <&gpio_ao 14 GPIO_ACTIVE_HIGH>; power-off-delay-ms = <100>; power-on-delay-ms = <300>; reset-assert-ms = <600>; reset-release-ms = <500>; ts-source = <0>; ts-port = <1>; ts-serial = <0>; tuner-compatible = "rafael,r848"; tuner-i2c-addr = <0x7a>; tuner-xtal-freq = <16000000>; }; }; /* Pinctrl: tsin_b (GPIOZ) paralel 8-bit */ &periphs_pinctrl { dvb_p_ts1_pins: dvb-p-ts1-pins { mux { groups = "tsin_b_sop_z", "tsin_b_valid_z", "tsin_b_clk_z", "tsin_b_din0_z", "tsin_b_din1", "tsin_b_din2", "tsin_b_din3", "tsin_b_din4", "tsin_b_din5", "tsin_b_din6", "tsin_b_din7"; function = "tsin_b"; }; }; dvb_s_ts1_pins: dvb-s-ts1-pins { mux { groups = "tsin_b_sop_z", "tsin_b_valid_z", "tsin_b_clk_z", "tsin_b_din0_z"; function = "tsin_b"; }; }; }; /* DVB donanim blogu (SM1 / S905X3) */ &{/soc} { dvb: dvb@ffd06000 { compatible = "amlogic,sm1-dvb"; reg = <0x0 0xffd06000 0x0 0x400>, <0x0 0xffd09000 0x0 0x2000>; reg-names = "ts", "async-fifo"; /* * EDGE_RISING: SM1'de AsyncFIFO donanımı edge pulse üretiyor. * LEVEL_HIGH kullanılırsa AsyncFIFO IRQ hiç gelmiyor (0 KB/s). * Kanıt: EDGE_RISING ile VLC kanal açıldı, LEVEL_HIGH ile 0 KB/s. */ interrupts = <GIC_SPI 23 IRQ_TYPE_EDGE_RISING>, /* demux0 */ <GIC_SPI 5 IRQ_TYPE_EDGE_RISING>, /* demux1 */ <GIC_SPI 21 IRQ_TYPE_EDGE_RISING>, /* demux2 */ <GIC_SPI 19 IRQ_TYPE_EDGE_RISING>, /* asyncfifo0 */ <GIC_SPI 25 IRQ_TYPE_EDGE_RISING>; /* asyncfifo1 */ interrupt-names = "demux0", "demux1", "demux2", "asyncfifo0", "asyncfifo1"; /* Android DTB doğrulaması: sıra demux → ahbarb0 → parser_top */ clocks = <&clkc CLKID_DEMUX>, <&clkc CLKID_AHB_ARB0>, <&clkc CLKID_PARSER>; clock-names = "demux", "ahbarb0", "parser_top"; /* meson-g12a-reset.h'dan doğrulanmış ID'ler: * RESET_DEMUX=33 ↔ vendor RESET1[bit1] (RESET_DEMUXSTB) * RESET_ASYNC0=203 ↔ vendor RESET6[bit11] * RESET_ASYNC1=204 ↔ vendor RESET6[bit12] * RESET_DEMUX_TOP=105 ↔ kapsamlı STB reset */ resets = <&reset RESET_DEMUX>, <&reset RESET_ASYNC0>, <&reset RESET_ASYNC1>, <&reset RESET_DEMUX_TOP>; reset-names = "demux", "asyncfifo", "asyncfifo1", "demux-top"; pinctrl-0 = <&dvb_p_ts1_pins>; pinctrl-1 = <&dvb_s_ts1_pins>; pinctrl-names = "default", "serial"; dma-coherent; status = "okay"; #address-cells = <1>; #size-cells = <0>; dvb-frontends = <&frontend0>; tsin_a: tsin@0 { reg = <0>; status = "disabled"; }; tsin_b: tsin@1 { reg = <1>; status = "okay"; }; }; }; /* Ethernet */ ðmac { status = "okay"; phy-handle = <&internal_ephy>; phy-mode = "rmii"; }; // SPDX-License-Identifier: (GPL-2.0+ OR MIT) /dts-v1/; #include "meson-sm1-ac2xx.dtsi" #include <dt-bindings/gpio/gpio.h> #include <dt-bindings/gpio/meson-g12a-gpio.h> #include <dt-bindings/interrupt-controller/irq.h> #include <dt-bindings/interrupt-controller/arm-gic.h> #include <dt-bindings/clock/g12a-clkc.h> / { compatible = "magicsee,c500-pro", "amlogic,sm1"; model = "MagicSee C500 Pro"; memory@0 { device_type = "memory"; reg = <0x0 0x0 0x0 0x80000000>; /* 2GB */ }; aliases { i2c2 = &i2c2; }; }; /* I2C2: AVL6261 frontend */ &i2c2 { status = "okay"; pinctrl-0 = <&i2c2_sda_z_pins>, <&i2c2_sck_z_pins>; pinctrl-names = "default"; clock-frequency = <100000>; frontend0: dvb-frontend@14 { compatible = "availink,avl6261"; reg = <0x14>; status = "okay"; reset-gpios = <&gpio GPIOZ_1 GPIO_ACTIVE_LOW>; power-gpios = <&gpio GPIOZ_0 GPIO_ACTIVE_HIGH>; ts-source = <0>; ts-port = <1>; ts-serial = <0>; /* GPIO timing */ power-off-delay-ms = <50>; power-on-delay-ms = <50>; reset-assert-ms = <600>; reset-release-ms = <200>; }; }; &periphs_pinctrl { dvb_p_ts1_pins: dvb-p-ts1-pins { mux { groups = "tsin_b_sop_z", "tsin_b_valid_z", "tsin_b_clk_z", "tsin_b_din0_z", "tsin_b_din1", "tsin_b_din2", "tsin_b_din3", "tsin_b_din4", "tsin_b_din5", "tsin_b_din6", "tsin_b_din7"; function = "tsin_b"; }; }; dvb_s_ts1_pins: dvb-s-ts1-pins { mux { groups = "tsin_b_sop_z", "tsin_b_valid_z", "tsin_b_clk_z", "tsin_b_din0_z"; function = "tsin_b"; }; }; }; /* DVB donanım bloğu */ &{/soc} { dvb: dvb@ffd06000 { compatible = "amlogic,sm1-dvb"; reg = <0x0 0xffd06000 0x0 0x400>, <0x0 0xffd09000 0x0 0x2000>; reg-names = "ts", "async-fifo"; interrupts = <GIC_SPI 23 IRQ_TYPE_EDGE_RISING>, /* dmx0: GIC HW 55, Linux 38 */ <GIC_SPI 5 IRQ_TYPE_EDGE_RISING>, /* dmx1: GIC HW 37, Linux 39 */ <GIC_SPI 21 IRQ_TYPE_EDGE_RISING>, /* dmx2: GIC HW 53, Linux 40 */ <GIC_SPI 19 IRQ_TYPE_EDGE_RISING>, /* asyncfifo0: GIC HW 51, Linux 41 */ <GIC_SPI 25 IRQ_TYPE_EDGE_RISING>; /* asyncfifo1: GIC HW 57, Linux 42 */ clocks = <&clkc CLKID_DEMUX>, <&clkc CLKID_PARSER>, <&clkc CLKID_AHB_ARB0>; clock-names = "demux", "parser_top", "ahbarb0"; status = "okay"; /* pinctrl-0 = default (paralel), pinctrl-1 = serial */ pinctrl-0 = <&dvb_p_ts1_pins>; pinctrl-1 = <&dvb_s_ts1_pins>; pinctrl-names = "parallel", "serial"; amlogic,num-filters = <32>; dma-coherent; dvb-frontends = <&frontend0>; /* * tsin_a: SM1'de sadece 1-bit serial. 8-bit paralel yok. * tsin_a_din4..7 grupları SM1 pinctrl'de tanımsız → disabled. */ tsin_a: tsin@0 { reg = <0>; status = "disabled"; }; /* * tsin_b: AVL6862 paralel 8-bit TS çıkışı buraya bağlı. * SM1'de tek 8-bit paralel TS girişi tsin_b'dir. */ tsin_b: tsin@1 { reg = <1>; amlogic,ts-bus-width = <8>; status = "okay"; }; }; }; /* Ethernet */ ðmac { status = "okay"; phy-handle = <&internal_ephy>; phy-mode = "rmii"; };yaml

C

Display More# SPDX-License-Identifier: (GPL-2.0-only OR BSD-2-Clause) %YAML 1.2 --- $id: http://devicetree.org/schemas/media/amlogic,meson-dvb.yaml $schema: http://devicetree.org/meta-schemas/core.yaml title: Amlogic Meson DVB/TS Hardware Demultiplexer maintainers: - Neil Armstrong <[email='[email protected]'][/email]> description: | The Amlogic Meson SoC family includes a hardware DVB/TS demultiplexer block (STB) capable of processing MPEG-2 transport streams. The block provides: - Up to 3 independent demux cores with 32 PID filters each - Up to 2 serial-to-parallel (S2P) TS input converters - Up to 2 AsyncFIFO DMA engines for DVR recording paths - CI+ descrambler (SM1/G12B only) - Software-based section filtering via dvb_dmx_swfilter() The AsyncFIFO engines receive raw TS data and deliver it to the Linux DVB core via dvb_dmx_swfilter(). Hardware section DMA is not used on SM1 (S905X3) and later SoCs; all PID/section filtering is performed in software. properties: compatible: oneOf: - items: - const: amlogic,sm1-dvb description: S905X3 (SM1), 3 demux, 2 AsyncFIFO, CI+ support - items: - const: amlogic,g12b-dvb description: S922X (G12B), 3 demux, 2 AsyncFIFO, CI+ support - items: - const: amlogic,g12a-dvb description: S905X2 (G12A), 3 demux, 2 AsyncFIFO - items: - const: amlogic,gxm-dvb description: S912 (GXM), 3 demux, 2 AsyncFIFO - items: - const: amlogic,gxl-dvb description: S905X/S905D (GXL), 3 demux, 2 AsyncFIFO - items: - const: amlogic,gxbb-dvb description: S905 (GXBB), 3 demux, 2 AsyncFIFO reg: items: - description: TS input control registers (TS_IN, S2P, STB_TOP_CONFIG) - description: AsyncFIFO DMA registers (async_fifo2 + async_fifo) minItems: 1 maxItems: 2 reg-names: items: - const: ts - const: async-fifo minItems: 1 maxItems: 2 interrupts: items: - description: Demux core 0 interrupt - description: Demux core 1 interrupt - description: Demux core 2 interrupt - description: AsyncFIFO 0 fill interrupt - description: AsyncFIFO 1 fill interrupt minItems: 3 maxItems: 5 interrupt-names: items: - const: demux0 - const: demux1 - const: demux2 - const: asyncfifo0 - const: asyncfifo1 minItems: 3 maxItems: 5 clocks: items: - description: STB/demux core clock - description: AHB arbiter clock - description: TS parser top clock minItems: 1 maxItems: 3 clock-names: items: - const: demux - const: ahbarb0 - const: parser_top minItems: 1 maxItems: 3 resets: items: - description: Demux core reset - description: AsyncFIFO 0 reset - description: AsyncFIFO 1 reset - description: Demux top reset minItems: 1 maxItems: 4 reset-names: items: - const: demux - const: asyncfifo - const: asyncfifo1 - const: demux-top minItems: 1 maxItems: 4 pinctrl-0: description: | TS input pin state. For parallel 8-bit mode (tsin_b) this must include all data, clock, SOP and valid signal groups. pinctrl-1: description: | TS serial input pin state. For single-bit serial mode (tsin_b din0). pinctrl-names: items: - const: default - const: serial minItems: 1 dma-coherent: true '#address-cells': const: 1 '#size-cells': const: 0 dvb-frontends: $ref: /schemas/types.yaml#/definitions/phandle-array description: | List of phandles to DVB frontend (demodulator) device nodes. Each frontend node must define ts-source (demux index) and ts-port (physical TS input port index) properties. minItems: 1 maxItems: 4 patternProperties: "^tsin@[0-9]+$": type: object description: | TS input sub-node. One node per physical TS input port. Disabled nodes are ignored by the driver. properties: reg: description: TS input port index (0 = tsin_a, 1 = tsin_b) minimum: 0 maximum: 3 amlogic,ts-bus-width: $ref: /schemas/types.yaml#/definitions/uint32 description: | TS data bus width in bits. 1 for serial mode, 8 for parallel. enum: [1, 8] default: 1 status: enum: [okay, disabled] required: - reg required: - compatible - reg - reg-names - interrupts - clocks - clock-names additionalProperties: false examples: - | #include <dt-bindings/interrupt-controller/irq.h> #include <dt-bindings/interrupt-controller/arm-gic.h> #include <dt-bindings/clock/g12a-clkc.h> #include <dt-bindings/reset/amlogic,meson-g12a-reset.h> /* SM1 (S905X3) — MeCool K5 */ dvb: dvb@ffd06000 { compatible = "amlogic,sm1-dvb"; reg = <0x0 0xffd06000 0x0 0x400>, <0x0 0xffd09000 0x0 0x2000>; reg-names = "ts", "async-fifo"; interrupts = <GIC_SPI 23 IRQ_TYPE_EDGE_RISING>, <GIC_SPI 5 IRQ_TYPE_EDGE_RISING>, <GIC_SPI 21 IRQ_TYPE_EDGE_RISING>, <GIC_SPI 19 IRQ_TYPE_EDGE_RISING>, <GIC_SPI 25 IRQ_TYPE_EDGE_RISING>; interrupt-names = "demux0", "demux1", "demux2", "asyncfifo0", "asyncfifo1"; clocks = <&clkc CLKID_DEMUX>, <&clkc CLKID_AHB_ARB0>, <&clkc CLKID_PARSER>; clock-names = "demux", "ahbarb0", "parser_top"; resets = <&reset RESET_DEMUX>, <&reset RESET_ASYNC0>, <&reset RESET_ASYNC1>, <&reset RESET_DEMUX_TOP>; reset-names = "demux", "asyncfifo", "asyncfifo1", "demux-top"; pinctrl-0 = <&dvb_p_ts1_pins>; pinctrl-1 = <&dvb_s_ts1_pins>; pinctrl-names = "default", "serial"; dma-coherent; status = "okay"; #address-cells = <1>; #size-cells = <0>; dvb-frontends = <&frontend0>; tsin_a: tsin@0 { reg = <0>; status = "disabled"; }; tsin_b: tsin@1 { reg = <1>; amlogic,ts-bus-width = <8>; status = "okay"; }; }; -

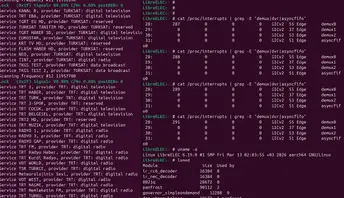

Amlogic 5.15 kernel hw demux driver for s905x3 - HW section filter doesn't work in hardware on SM1, using DVR+SW path based on IRQs dmx irq (40/41/42) = 0 ← NEVER fires dvr irq (43/44) = increasing ← Only AsyncFIFO is working.

Code

Display MoreVLC streaming simultaneously from 2 frontends with Magicsee C500 Pro CoreELEC TVHeadend CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 13: 19576 24344 23713 24193 GIC-0 26 Level arch_timer 21: 25135 0 0 8057 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 0 0 0 0 GIC-0 51 Edge dvr irq 44: 429 0 0 0 GIC-0 57 Edge dvr irq CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 21: 25135 0 0 8265 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 217 0 0 0 GIC-0 51 Edge dvr irq 44: 1410 0 0 0 GIC-0 57 Edge dvr irq IPI1: 12614 20247 13735 20058 Function call interrupts CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 21: 25135 0 0 8275 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 293 0 0 0 GIC-0 51 Edge dvr irq 44: 1459 0 0 0 GIC-0 57 Edge dvr irq 46: 82 0 37868 0 GIC-0 40 Level eth0 CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 21: 25135 0 0 8277 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 340 0 0 0 GIC-0 51 Edge dvr irq 44: 1489 0 0 0 GIC-0 57 Edge dvr irq IPI0: 1808 4338 3600 5300 Rescheduling interrupts CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 21: 25135 0 0 8313 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 368 0 0 0 GIC-0 51 Edge dvr irq 44: 1507 0 0 0 GIC-0 57 Edge dvr irq IPI0: 1811 4343 3603 5305 Rescheduling interrupts CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 21: 25135 0 0 8315 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 395 0 0 0 GIC-0 51 Edge dvr irq 44: 1525 0 0 0 GIC-0 57 Edge dvr irq IPI0: 1814 4349 3607 5307 Rescheduling interrupts CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 21: 25135 0 0 8317 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 436 0 0 0 GIC-0 51 Edge dvr irq 44: 1551 0 0 0 GIC-0 57 Edge dvr irq 50: 0 370 0 0 GIC-0 235 Edge hdmi_aocecb IPI0: 1816 4355 3612 5309 Rescheduling interrupts CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 21: 25135 0 0 8319 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 486 0 0 0 GIC-0 51 Edge dvr irq 44: 1584 0 0 0 GIC-0 57 Edge dvr irq 50: 0 374 0 0 GIC-0 235 Edge hdmi_aocecb IPI0: 1822 4360 3615 5312 Rescheduling interrupts CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 13: 28312 35075 45342 34751 GIC-0 26 Level arch_timer 21: 25135 0 0 8321 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 554 0 0 0 GIC-0 51 Edge dvr irq 44: 1627 0 0 0 GIC-0 57 Edge dvr irq IPI0: 1827 4365 3618 5316 Rescheduling interrupts IPI1: 13279 21087 14536 20840 Function call interrupts CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 13: 28451 35142 45718 34975 GIC-0 26 Level arch_timer 21: 25135 0 0 8323 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 578 0 0 0 GIC-0 51 Edge dvr irq 44: 1642 0 0 0 GIC-0 57 Edge dvr irq IPI0: 1832 4369 3623 5319 Rescheduling interrupts CoreELEC:~ # ------------------------------------------------------------------------------------- Simultaneous 2 frontend channel scan on CoreELEC CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 13: 45663 53316 89967 65378 GIC-0 26 Level arch_timer 21: 25135 0 0 8696 GIC-0 62 Level xhci-hcd:usb1 26: 16351 0 0 0 GIC-0 71 Edge ffd1c000.i2c 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 2912 0 0 0 GIC-0 51 Edge dvr irq 44: 4579 0 0 0 GIC-0 57 Edge dvr irq IPI0: 1929 4481 3775 5444 Rescheduling interrupts CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 13: 45850 53448 90124 65515 GIC-0 26 Level arch_timer 21: 25135 0 0 8701 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 2930 0 0 0 GIC-0 51 Edge dvr irq 44: 4596 0 0 0 GIC-0 57 Edge dvr irq IPI0: 1935 4484 3779 5448 Rescheduling interrupts CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 13: 45965 53588 90386 65680 GIC-0 26 Level arch_timer 21: 25135 0 0 8704 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 2943 0 0 0 GIC-0 51 Edge dvr irq 44: 4614 0 0 0 GIC-0 57 Edge dvr irq IPI0: 1938 4491 3782 5453 Rescheduling interrupts CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 13: 46114 53726 90649 65998 GIC-0 26 Level arch_timer 21: 25135 0 0 8718 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 2956 0 0 0 GIC-0 51 Edge dvr irq 44: 4635 0 0 0 GIC-0 57 Edge dvr irq IPI0: 1943 4496 3785 5458 Rescheduling interrupts IPI1: 17887 27934 23030 27853 Function call interrupts CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 13: 46307 53827 90973 66348 GIC-0 26 Level arch_timer 21: 25135 0 0 8726 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 2972 0 0 0 GIC-0 51 Edge dvr irq 44: 4663 0 0 0 GIC-0 57 Edge dvr irq 65: 90137 0 0 0 GIC-0 221 Level ffe03000.sdio IPI0: 1946 4502 3791 5461 Rescheduling interrupts CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 13: 46368 53927 91084 66564 GIC-0 26 Level arch_timer 21: 25135 0 0 8729 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 2980 0 0 0 GIC-0 51 Edge dvr irq 44: 4675 0 0 0 GIC-0 57 Edge dvr irq 65: 90137 0 0 0 GIC-0 221 Level ffe03000.sdio IPI0: 1952 4507 3794 5464 Rescheduling interrupts CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 21: 25135 0 0 8731 GIC-0 62 Level xhci-hcd:usb1 24: 12353 0 0 0 GIC-0 247 Edge ffd1d000.i2c 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 2995 0 0 0 GIC-0 51 Edge dvr irq 44: 4686 0 0 0 GIC-0 57 Edge dvr irq IPI0: 1955 4510 3798 5469 Rescheduling interrupts CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 13: 46729 54404 91532 66780 GIC-0 26 Level arch_timer 21: 25135 0 0 8752 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 3007 0 0 0 GIC-0 51 Edge dvr irq 44: 4694 0 0 0 GIC-0 57 Edge dvr irq IPI0: 1960 4513 3800 5475 Rescheduling interrupts CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 21: 25135 0 0 8772 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 3028 0 0 0 GIC-0 51 Edge dvr irq 44: 4702 0 0 0 GIC-0 57 Edge dvr irq IPI0: 1965 4518 3803 5484 Rescheduling interrupts CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 21: 25135 0 0 8777 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 3050 0 0 0 GIC-0 51 Edge dvr irq 44: 4710 0 0 0 GIC-0 57 Edge dvr irq CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 21: 25135 0 0 8783 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 3072 0 0 0 GIC-0 51 Edge dvr irq 44: 4713 0 0 0 GIC-0 57 Edge dvr irq IPI0: 1971 4532 3812 5492 Rescheduling interrupts CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 21: 25135 0 0 8908 GIC-0 62 Level xhci-hcd:usb1 26: 19556 0 0 0 GIC-0 71 Edge ffd1c000.i2c 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 3328 0 0 0 GIC-0 51 Edge dvr irq 44: 4934 0 0 0 GIC-0 57 Edge dvr irq IPI0: 1977 4544 3820 5507 Rescheduling interrupts CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 21: 25135 0 0 8916 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 3357 0 0 0 GIC-0 51 Edge dvr irq 44: 4952 0 0 0 GIC-0 57 Edge dvr irq 46: 82 0 95174 0 GIC-0 40 Level eth0 IPI0: 1982 4548 3824 5511 Rescheduling interrupts IPI1: 18670 29081 23923 29053 Function call interrupts CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 13: 49241 57192 94753 70414 GIC-0 26 Level arch_timer 21: 25135 0 0 8921 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 3399 0 0 0 GIC-0 51 Edge dvr irq 44: 5011 0 0 0 GIC-0 57 Edge dvr irq 65: 90337 0 0 0 GIC-0 221 Level ffe03000.sdio IPI0: 1987 4552 3828 5514 Rescheduling interrupts CoreELEC:~ # cat /proc/interrupts | grep -i "dmx\|dvr\|55\|37\|53\|51" 13: 49437 57608 95008 71083 GIC-0 26 Level arch_timer 21: 25135 0 0 8943 GIC-0 62 Level xhci-hcd:usb1 40: 0 0 0 0 GIC-0 55 Edge dmx irq 41: 0 0 0 0 GIC-0 37 Edge dmx irq 42: 0 0 0 0 GIC-0 53 Edge dmx irq 43: 3414 0 0 0 GIC-0 51 Edge dvr irq 44: 5076 0 0 0 GIC-0 57 Edge dvr irq IPI0: 1992 4555 3833 5518 Rescheduling interrupts CoreELEC:~ # -

taki Thanks for sharing the patches, they are interesting reading! .. once decrypted from Turkish to English

Some of the comments you've made are valuable. I was seeing an attach issue with MxL608 behind an AVL6762 i2c repeater when working on my O2.cz box, and while trial and error with Claude eventually figured out a "fix" and theorised an explanation, one of your comments explains the actual problem and better/correct solution.

-

taki it might be a bug that I found when porting vendor driver to mainline.

In aml_dmx.c You will find sunch code:Code

Display More#define DEMUX_INT_MASK\ ((0<<(AUDIO_SPLICING_POINT)) |\ (0<<(VIDEO_SPLICING_POINT)) |\ (1<<(OTHER_PES_READY)) |\ (1<<(SUB_PES_READY)) |\ (1<<(SECTION_BUFFER_READY)) |\ (0<<(OM_CMD_READ_PENDING)) |\ (1<<(TS_ERROR_PIN)) |\ (1<<(NEW_PDTS_READY)) |\ (0<<(DUPLICATED_PACKET)) |\ (0<<(DIS_CONTINUITY_PACKET)))Change 1<<(NEW_PDTS_READY) to 0<<(NEW_PDTS_READY) and check if it helps.

For some reason this NEW_PDTS_READY interrupt source triggers at a very high rate and the kernel disables it. Disabling this interrupt is only a workaround but I don't know how to fix that better. And by looking at the code this interrupt source is not relevant.

The other thing is that when using tvheadend I also have no dmx_irqs (only dvr_irqs).

But when using dvbv5-zap (dvbv5-zap -c dvb_channel.conf -r "Some channel") I get dmx_irqs: -

taki it might be a bug that I found when porting vendor driver to mainline.

In aml_dmx.c You will find sunch code:Code

Display More#define DEMUX_INT_MASK\ ((0<<(AUDIO_SPLICING_POINT)) |\ (0<<(VIDEO_SPLICING_POINT)) |\ (1<<(OTHER_PES_READY)) |\ (1<<(SUB_PES_READY)) |\ (1<<(SECTION_BUFFER_READY)) |\ (0<<(OM_CMD_READ_PENDING)) |\ (1<<(TS_ERROR_PIN)) |\ (1<<(NEW_PDTS_READY)) |\ (0<<(DUPLICATED_PACKET)) |\ (0<<(DIS_CONTINUITY_PACKET)))Change 1<<(NEW_PDTS_READY) to 0<<(NEW_PDTS_READY) and check if it helps.

For some reason this NEW_PDTS_READY interrupt source triggers at a very high rate and the kernel disables it. Disabling this interrupt is only a workaround but I don't know how to fix that better. And by looking at the code this interrupt source is not relevant.

The other thing is that when using tvheadend I also have no dmx_irqs (only dvr_irqs).

But when using dvbv5-zap (dvbv5-zap -c dvb_channel.conf -r "Some channel") I get dmx_irqs:I will try.

# Terminal 1 — dvbv5-zap

dvbv5-zap -c /storage/.kodi/addons/service.tvheadend43/dvb-scan/dvb-s/Turksat-4A-42.0E \

-r "TRT 1" &# (lock + scan)

sleep 10# Terminal 2 — IRQ

cat /proc/interrupts | grep -E "dmx|dvr"

sleep 5

cat /proc/interrupts | grep -E "dmx|dvr"If the DMX IRQ is increasing → the HW section filter is also working in SM1, and TVHeadend is preferring the DVR path.

-

For testing, I tried kernel 5.15 on coreelec. I scanned dvbv5 channels on both frontends at the same time. I searched with ts0 avl6762demod +mxl 608 tuner GIC-0 55 Edge, ts1 avl6261 demo and av2018 GIC-0 37 Edge. bingo demux irq data increasing. Now it's time to focus on the mainline driver. The hardware was working.

CoreELEC:~ # cat /proc/interrupts | grep -E "dmx|dvr"

CoreELEC:~ # cat /proc/interrupts | grep -E "dmx|dvr"

40: 360 0 0 0 GIC-0 55 Edge dmx irq

41: 45 0 0 0 GIC-0 37 Edge dmx irq

42: 0 0 0 0 GIC-0 53 Edge dmx irq

43: 0 0 0 0 GIC-0 51 Edge dvr irq

44: 0 0 0 0 GIC-0 57 Edge dvr irq

CoreELEC:~ # cat /proc/interrupts | grep -E "dmx|dvr"

40: 375 0 0 0 GIC-0 55 Edge dmx irq

41: 57 0 0 0 GIC-0 37 Edge dmx irq

42: 0 0 0 0 GIC-0 53 Edge dmx irq

43: 0 0 0 0 GIC-0 51 Edge dvr irq

44: 0 0 0 0 GIC-0 57 Edge dvr irq

CoreELEC:~ # cat /proc/interrupts | grep -E "dmx|dvr"

40: 485 0 0 0 GIC-0 55 Edge dmx irq

41: 203 0 0 0 GIC-0 37 Edge dmx irq

42: 0 0 0 0 GIC-0 53 Edge dmx irq

43: 0 0 0 0 GIC-0 51 Edge dvr irq

44: 0 0 0 0 GIC-0 57 Edge dvr irq

CoreELEC:~ # cat /proc/interrupts | grep -E "dmx|dvr"

40: 485 0 0 0 GIC-0 55 Edge dmx irq

41: 350 0 0 0 GIC-0 37 Edge dmx irq

42: 0 0 0 0 GIC-0 53 Edge dmx irq

43: 0 0 0 0 GIC-0 51 Edge dvr irq

44: 0 0 0 0 GIC-0 57 Edge dvr irq

CoreELEC:~ # -

I think that TVHeadend is just requesting the whole TS stream that contains all of the channels to be able to provide all channels from one mux to multiple clients. And in such situation the demux driver does not have to do demuxing thus there is no dmx irqs. Does that make sense ?

-

That's exactly how it works.

-

Based on the information from rozpruwacz, I think I managed to get the hardware PID filter working. The software filter is already running. From what I understand, many DVB players prefer the DVR line. I’m not sure, but Amlogic’s own player checks the DMX line. It’s a pretty complicated topic, though. The driver now shows the interrupt names as well. There are no segfaults. Now I just need to check if the second DMX line is working. I also added some code to see if the reset and power GPIOs are being probed by the driver. This way, we can determine whether the new device’s GPIO pins are being connected by the driver. There’s a section in the driver that outputs a lot of debug messages. These will be minimized once the driver matures. There are two key issues and approaches here.

1-It seems highly unlikely that 90% of the demodulators and tuners used in Mainline Amlogic boxes will be accepted by Mainline, or that someone will take the time to fix and integrate the drivers according to Mainline standards. Therefore, it makes more sense to use the drivers that work on our devices as add-ons; otherwise, we’d have to constantly write new patches for the main kernel, which is updated with every build.

2-There are latency and waiting issues on the I2C bus caused by the demod/tuner connection in Amlogic hardware. Even if the driver works, it may fail on the next boot and work on the one after that. This is related to the hardware’s frontend architecture and requires very fine-tuning.

While I was at it, I added nim_socket. Maybe Engima 2 compilers will be needed in the future. There are no upsides to libreelec.

ibreELEC:~ # uname -a

Linux LibreELEC 6.19.0 #1 SMP Fri Mar 13 02:03:55 +03 2026 aarch64 GNU/Linux

LibreELEC:~ # cat /proc/bus/nim_sockets

NIM Socket 0:

Type: DVB-T2

Name: Availink avl6862

Frontend_Device: 0

I2C_Device: 3

Has_Outputs: yes

Mode 0: DVB-S

Mode 1: DVB-T

Mode 2: DVB-C

Internally_Connectable: 0 -