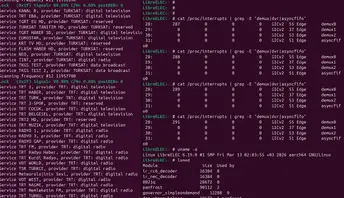

To detect the reset power, i2c pin and active ts pins of the dvb driver, first connect to the android own software with adb and cat /sys/kernel/debug/pinctrl/*/pinmux-pins

Get the device information with cat /sys/kernel/debug/pinctrl/*/pinmux-functions and edit the mainline dts accordingly. You may need to shut down some nodes or redirect them to the correct pin due to pin conflict. I gave the driver as an addon. Copy the AVL6862 folder under LibreELEC.tv/packages/linux-driver-addons/dvb/ and add PROJECT=Amlogic DEVICE=AMLGX ARCH=aarch64 ./scripts/create_addon AVL6862 compile. Of course, if the dts is not correct, the driver probe will not occur. Maybe you can take it one step further.good luck

sample dts

// SPDX-License-Identifier: (GPL-2.0+ OR MIT)

/*

* MeCool K5 DVB DTS - V2.57

*

* V2.49 değişiklikleri:

* - Clock sırası Android DTB ile uyumlu: demux, ahbarb0, parser_top

* - Resets: RESET_DEMUX/ASYNC0/ASYNC1/DEMUX_TOP (meson-g12a-reset.h)

* - Reset include eklendi

*

* Donanim:

* AVL6862 demod (Rafael R848 tuner)

* -> GPIOZ pinleri, tsin_b, 8-bit paralel -> SM1 TS1 (FEC_SEL=1)

* -> i2c3 (SDA=GPIOA_14, SCK=GPIOA_15)

* Reset : GPIOAO_10 (ACTIVE_LOW)

* Power : GPIOE_2 / aobus offset 14 (ACTIVE_HIGH)

*

* SM1 register haritasi (devmem2 dogrulandi):

* "ts" : 0xFFD06000-0xFFD063FF

* "async-fifo": 0xFFD09000-0xFFD0AFFF

*

* IRQ (GIC_SPI = GIC_HW - 32, IRQ_TYPE_EDGE_RISING zorunlu):

* GIC SPI 23 -> demux0 (HW55)

* GIC SPI 5 -> demux1 (HW37)

* GIC SPI 21 -> demux2 (HW53)

* GIC SPI 19 -> asyncfifo0 (HW51)

* GIC SPI 25 -> asyncfifo1 (HW57)

*

* ONEMLI: SM1'de EDGE_RISING kullan! LEVEL_HIGH ile

* AsyncFIFO IRQ gelmiyor → veri akışı tamamen durur.

*/

/dts-v1/;

#include "meson-sm1-ac2xx.dtsi"

#include <dt-bindings/gpio/gpio.h>

#include <dt-bindings/gpio/meson-g12a-gpio.h>

#include <dt-bindings/interrupt-controller/irq.h>

#include <dt-bindings/interrupt-controller/arm-gic.h>

#include <dt-bindings/clock/g12a-clkc.h>

#include <dt-bindings/reset/amlogic,meson-g12a-reset.h>

/ {

compatible = "videostrong,mecool-k5", "amlogic,sm1";

model = "VIDEOSTRONG MeCool K5";

memory@0 {

device_type = "memory";

reg = <0x0 0x0 0x0 0x80000000>; /* 2GB */

};

aliases {

i2c3 = &i2c3;

};

};

/* GPIOAO_10 (reset pini) ile cakisiyor */

&pwm_AO_ab {

status = "disabled";

};

/* I2C3: AVL6862 */

&i2c3 {

status = "okay";

pinctrl-0 = <&i2c3_sda_a_pins>, <&i2c3_sck_a_pins>;

pinctrl-names = "default";

clock-frequency = <100000>;

frontend0: dvb-frontend@14 {

compatible = "availink,avl6862";

reg = <0x14>;

status = "okay";

reset-gpios = <&gpio_ao 10 GPIO_ACTIVE_LOW>;

power-gpios = <&gpio_ao 14 GPIO_ACTIVE_HIGH>;

power-off-delay-ms = <100>;

power-on-delay-ms = <300>;

reset-assert-ms = <600>;

reset-release-ms = <500>;

ts-source = <0>;

ts-port = <1>;

ts-serial = <0>;

tuner-compatible = "rafael,r848";

tuner-i2c-addr = <0x7a>;

tuner-xtal-freq = <16000000>;

};

};

/* Pinctrl: tsin_b (GPIOZ) paralel 8-bit */

&periphs_pinctrl {

dvb_p_ts1_pins: dvb-p-ts1-pins {

mux {

groups = "tsin_b_sop_z",

"tsin_b_valid_z",

"tsin_b_clk_z",

"tsin_b_din0_z",

"tsin_b_din1",

"tsin_b_din2",

"tsin_b_din3",

"tsin_b_din4",

"tsin_b_din5",

"tsin_b_din6",

"tsin_b_din7";

function = "tsin_b";

};

};

dvb_s_ts1_pins: dvb-s-ts1-pins {

mux {

groups = "tsin_b_sop_z",

"tsin_b_valid_z",

"tsin_b_clk_z",

"tsin_b_din0_z";

function = "tsin_b";

};

};

};

/* DVB donanim blogu (SM1 / S905X3) */

&{/soc} {

dvb: dvb@ffd06000 {

compatible = "amlogic,sm1-dvb";

reg = <0x0 0xffd06000 0x0 0x400>,

<0x0 0xffd09000 0x0 0x2000>;

reg-names = "ts", "async-fifo";

/*

* EDGE_RISING: SM1'de AsyncFIFO donanımı edge pulse üretiyor.

* LEVEL_HIGH kullanılırsa AsyncFIFO IRQ hiç gelmiyor (0 KB/s).

* Kanıt: EDGE_RISING ile VLC kanal açıldı, LEVEL_HIGH ile 0 KB/s.

*/

interrupts = <GIC_SPI 23 IRQ_TYPE_EDGE_RISING>, /* demux0 */

<GIC_SPI 5 IRQ_TYPE_EDGE_RISING>, /* demux1 */

<GIC_SPI 21 IRQ_TYPE_EDGE_RISING>, /* demux2 */

<GIC_SPI 19 IRQ_TYPE_EDGE_RISING>, /* asyncfifo0 */

<GIC_SPI 25 IRQ_TYPE_EDGE_RISING>; /* asyncfifo1 */

interrupt-names = "demux0", "demux1", "demux2",

"asyncfifo0", "asyncfifo1";

/* Android DTB doğrulaması: sıra demux → ahbarb0 → parser_top */

clocks = <&clkc CLKID_DEMUX>,

<&clkc CLKID_AHB_ARB0>,

<&clkc CLKID_PARSER>;

clock-names = "demux", "ahbarb0", "parser_top";

/* meson-g12a-reset.h'dan doğrulanmış ID'ler:

* RESET_DEMUX=33 ↔ vendor RESET1[bit1] (RESET_DEMUXSTB)

* RESET_ASYNC0=203 ↔ vendor RESET6[bit11]

* RESET_ASYNC1=204 ↔ vendor RESET6[bit12]

* RESET_DEMUX_TOP=105 ↔ kapsamlı STB reset */

resets = <&reset RESET_DEMUX>,

<&reset RESET_ASYNC0>,

<&reset RESET_ASYNC1>,

<&reset RESET_DEMUX_TOP>;

reset-names = "demux", "asyncfifo", "asyncfifo1", "demux-top";

pinctrl-0 = <&dvb_p_ts1_pins>;

pinctrl-1 = <&dvb_s_ts1_pins>;

pinctrl-names = "default", "serial";

dma-coherent;

status = "okay";

#address-cells = <1>;

#size-cells = <0>;

dvb-frontends = <&frontend0>;

tsin_a: tsin@0 {

reg = <0>;

status = "disabled";

};

tsin_b: tsin@1 {

reg = <1>;

status = "okay";

};

};

};

/* Ethernet */

ðmac {

status = "okay";

phy-handle = <&internal_ephy>;

phy-mode = "rmii";

};

// SPDX-License-Identifier: (GPL-2.0+ OR MIT)

/dts-v1/;

#include "meson-sm1-ac2xx.dtsi"

#include <dt-bindings/gpio/gpio.h>

#include <dt-bindings/gpio/meson-g12a-gpio.h>

#include <dt-bindings/interrupt-controller/irq.h>

#include <dt-bindings/interrupt-controller/arm-gic.h>

#include <dt-bindings/clock/g12a-clkc.h>

/ {

compatible = "magicsee,c500-pro", "amlogic,sm1";

model = "MagicSee C500 Pro";

memory@0 {

device_type = "memory";

reg = <0x0 0x0 0x0 0x80000000>; /* 2GB */

};

aliases {

i2c2 = &i2c2;

};

};

/* I2C2: AVL6261 frontend */

&i2c2 {

status = "okay";

pinctrl-0 = <&i2c2_sda_z_pins>, <&i2c2_sck_z_pins>;

pinctrl-names = "default";

clock-frequency = <100000>;

frontend0: dvb-frontend@14 {

compatible = "availink,avl6261";

reg = <0x14>;

status = "okay";

reset-gpios = <&gpio GPIOZ_1 GPIO_ACTIVE_LOW>;

power-gpios = <&gpio GPIOZ_0 GPIO_ACTIVE_HIGH>;

ts-source = <0>;

ts-port = <1>;

ts-serial = <0>;

/* GPIO timing */

power-off-delay-ms = <50>;

power-on-delay-ms = <50>;

reset-assert-ms = <600>;

reset-release-ms = <200>;

};

};

&periphs_pinctrl {

dvb_p_ts1_pins: dvb-p-ts1-pins {

mux {

groups = "tsin_b_sop_z",

"tsin_b_valid_z",

"tsin_b_clk_z",

"tsin_b_din0_z",

"tsin_b_din1",

"tsin_b_din2",

"tsin_b_din3",

"tsin_b_din4",

"tsin_b_din5",

"tsin_b_din6",

"tsin_b_din7";

function = "tsin_b";

};

};

dvb_s_ts1_pins: dvb-s-ts1-pins {

mux {

groups = "tsin_b_sop_z",

"tsin_b_valid_z",

"tsin_b_clk_z",

"tsin_b_din0_z";

function = "tsin_b";

};

};

};

/* DVB donanım bloğu */

&{/soc} {

dvb: dvb@ffd06000 {

compatible = "amlogic,sm1-dvb";

reg = <0x0 0xffd06000 0x0 0x400>,

<0x0 0xffd09000 0x0 0x2000>;

reg-names = "ts", "async-fifo";

interrupts = <GIC_SPI 23 IRQ_TYPE_EDGE_RISING>, /* dmx0: GIC HW 55, Linux 38 */

<GIC_SPI 5 IRQ_TYPE_EDGE_RISING>, /* dmx1: GIC HW 37, Linux 39 */

<GIC_SPI 21 IRQ_TYPE_EDGE_RISING>, /* dmx2: GIC HW 53, Linux 40 */

<GIC_SPI 19 IRQ_TYPE_EDGE_RISING>, /* asyncfifo0: GIC HW 51, Linux 41 */

<GIC_SPI 25 IRQ_TYPE_EDGE_RISING>; /* asyncfifo1: GIC HW 57, Linux 42 */

clocks = <&clkc CLKID_DEMUX>,

<&clkc CLKID_PARSER>,

<&clkc CLKID_AHB_ARB0>;

clock-names = "demux", "parser_top", "ahbarb0";

status = "okay";

/* pinctrl-0 = default (paralel), pinctrl-1 = serial */

pinctrl-0 = <&dvb_p_ts1_pins>;

pinctrl-1 = <&dvb_s_ts1_pins>;

pinctrl-names = "parallel", "serial";

amlogic,num-filters = <32>;

dma-coherent;

dvb-frontends = <&frontend0>;

/*

* tsin_a: SM1'de sadece 1-bit serial. 8-bit paralel yok.

* tsin_a_din4..7 grupları SM1 pinctrl'de tanımsız → disabled.

*/

tsin_a: tsin@0 {

reg = <0>;

status = "disabled";

};

/*

* tsin_b: AVL6862 paralel 8-bit TS çıkışı buraya bağlı.

* SM1'de tek 8-bit paralel TS girişi tsin_b'dir.

*/

tsin_b: tsin@1 {

reg = <1>;

amlogic,ts-bus-width = <8>;

status = "okay";

};

};

};

/* Ethernet */

ðmac {

status = "okay";

phy-handle = <&internal_ephy>;

phy-mode = "rmii";

};

Display More

yaml

# SPDX-License-Identifier: (GPL-2.0-only OR BSD-2-Clause)

%YAML 1.2

---

$id: http://devicetree.org/schemas/media/amlogic,meson-dvb.yaml

$schema: http://devicetree.org/meta-schemas/core.yaml

title: Amlogic Meson DVB/TS Hardware Demultiplexer

maintainers:

- Neil Armstrong <[email='[email protected]'][/email]>

description: |

The Amlogic Meson SoC family includes a hardware DVB/TS demultiplexer

block (STB) capable of processing MPEG-2 transport streams. The block

provides:

- Up to 3 independent demux cores with 32 PID filters each

- Up to 2 serial-to-parallel (S2P) TS input converters

- Up to 2 AsyncFIFO DMA engines for DVR recording paths

- CI+ descrambler (SM1/G12B only)

- Software-based section filtering via dvb_dmx_swfilter()

The AsyncFIFO engines receive raw TS data and deliver it to the Linux

DVB core via dvb_dmx_swfilter(). Hardware section DMA is not used on

SM1 (S905X3) and later SoCs; all PID/section filtering is performed in

software.

properties:

compatible:

oneOf:

- items:

- const: amlogic,sm1-dvb

description: S905X3 (SM1), 3 demux, 2 AsyncFIFO, CI+ support

- items:

- const: amlogic,g12b-dvb

description: S922X (G12B), 3 demux, 2 AsyncFIFO, CI+ support

- items:

- const: amlogic,g12a-dvb

description: S905X2 (G12A), 3 demux, 2 AsyncFIFO

- items:

- const: amlogic,gxm-dvb

description: S912 (GXM), 3 demux, 2 AsyncFIFO

- items:

- const: amlogic,gxl-dvb

description: S905X/S905D (GXL), 3 demux, 2 AsyncFIFO

- items:

- const: amlogic,gxbb-dvb

description: S905 (GXBB), 3 demux, 2 AsyncFIFO

reg:

items:

- description: TS input control registers (TS_IN, S2P, STB_TOP_CONFIG)

- description: AsyncFIFO DMA registers (async_fifo2 + async_fifo)

minItems: 1

maxItems: 2

reg-names:

items:

- const: ts

- const: async-fifo

minItems: 1

maxItems: 2

interrupts:

items:

- description: Demux core 0 interrupt

- description: Demux core 1 interrupt

- description: Demux core 2 interrupt

- description: AsyncFIFO 0 fill interrupt

- description: AsyncFIFO 1 fill interrupt

minItems: 3

maxItems: 5

interrupt-names:

items:

- const: demux0

- const: demux1

- const: demux2

- const: asyncfifo0

- const: asyncfifo1

minItems: 3

maxItems: 5

clocks:

items:

- description: STB/demux core clock

- description: AHB arbiter clock

- description: TS parser top clock

minItems: 1

maxItems: 3

clock-names:

items:

- const: demux

- const: ahbarb0

- const: parser_top

minItems: 1

maxItems: 3

resets:

items:

- description: Demux core reset

- description: AsyncFIFO 0 reset

- description: AsyncFIFO 1 reset

- description: Demux top reset

minItems: 1

maxItems: 4

reset-names:

items:

- const: demux

- const: asyncfifo

- const: asyncfifo1

- const: demux-top

minItems: 1

maxItems: 4

pinctrl-0:

description: |

TS input pin state. For parallel 8-bit mode (tsin_b) this must

include all data, clock, SOP and valid signal groups.

pinctrl-1:

description: |

TS serial input pin state. For single-bit serial mode (tsin_b din0).

pinctrl-names:

items:

- const: default

- const: serial

minItems: 1

dma-coherent: true

'#address-cells':

const: 1

'#size-cells':

const: 0

dvb-frontends:

$ref: /schemas/types.yaml#/definitions/phandle-array

description: |

List of phandles to DVB frontend (demodulator) device nodes.

Each frontend node must define ts-source (demux index) and

ts-port (physical TS input port index) properties.

minItems: 1

maxItems: 4

patternProperties:

"^tsin@[0-9]+$":

type: object

description: |

TS input sub-node. One node per physical TS input port.

Disabled nodes are ignored by the driver.

properties:

reg:

description: TS input port index (0 = tsin_a, 1 = tsin_b)

minimum: 0

maximum: 3

amlogic,ts-bus-width:

$ref: /schemas/types.yaml#/definitions/uint32

description: |

TS data bus width in bits. 1 for serial mode, 8 for parallel.

enum: [1, 8]

default: 1

status:

enum: [okay, disabled]

required:

- reg

required:

- compatible

- reg

- reg-names

- interrupts

- clocks

- clock-names

additionalProperties: false

examples:

- |

#include <dt-bindings/interrupt-controller/irq.h>

#include <dt-bindings/interrupt-controller/arm-gic.h>

#include <dt-bindings/clock/g12a-clkc.h>

#include <dt-bindings/reset/amlogic,meson-g12a-reset.h>

/* SM1 (S905X3) — MeCool K5 */

dvb: dvb@ffd06000 {

compatible = "amlogic,sm1-dvb";

reg = <0x0 0xffd06000 0x0 0x400>,

<0x0 0xffd09000 0x0 0x2000>;

reg-names = "ts", "async-fifo";

interrupts = <GIC_SPI 23 IRQ_TYPE_EDGE_RISING>,

<GIC_SPI 5 IRQ_TYPE_EDGE_RISING>,

<GIC_SPI 21 IRQ_TYPE_EDGE_RISING>,

<GIC_SPI 19 IRQ_TYPE_EDGE_RISING>,

<GIC_SPI 25 IRQ_TYPE_EDGE_RISING>;

interrupt-names = "demux0", "demux1", "demux2",

"asyncfifo0", "asyncfifo1";

clocks = <&clkc CLKID_DEMUX>,

<&clkc CLKID_AHB_ARB0>,

<&clkc CLKID_PARSER>;

clock-names = "demux", "ahbarb0", "parser_top";

resets = <&reset RESET_DEMUX>,

<&reset RESET_ASYNC0>,

<&reset RESET_ASYNC1>,

<&reset RESET_DEMUX_TOP>;

reset-names = "demux", "asyncfifo", "asyncfifo1", "demux-top";

pinctrl-0 = <&dvb_p_ts1_pins>;

pinctrl-1 = <&dvb_s_ts1_pins>;

pinctrl-names = "default", "serial";

dma-coherent;

status = "okay";

#address-cells = <1>;

#size-cells = <0>;

dvb-frontends = <&frontend0>;

tsin_a: tsin@0 {

reg = <0>;

status = "disabled";

};

tsin_b: tsin@1 {

reg = <1>;

amlogic,ts-bus-width = <8>;

status = "okay";

};

};

Display More